Изобретение относится к импульсной технике, предназначено для измерения

уровня нелинейных искажений быстродействующих аналого-цифровых преобразователей (АЦП) и может быть использовано в системах контроля нелинейных искажений, вносимых АЦП в динамическом режиме.

Известно устройство для измерения нелинейности АЦП, содержащее первый и второй генераторы гармонических сигналов, аналоговый сумматор, поверяемый АЦП, второй АЦП, вычитатель, цифроаналоговый преобразователь (ЦАП), фильтр нижних частот (ФНЧ), анализатор спектра (АС) [1]. Недостатком этого устройства является ограничение частотного диапазона измерения, за счет наличия в схеме вычитателя и ЦАП, которые обеспечивают требуемую точность измерения в ущерб диапазону рабочих частот поверяемого АЦП.

Наиболее близким по технической сущности к заявляемому устройству является измеритель нелинейности АЦП, содержащий первый и второй генераторы гармонических сигналов, аналоговый сумматор, мультиплексор, АЦП, демультиплексор, первый и второй элементы задержки, цифровой сумматор, последовательно соединенные вычитающее устройство, ЦАП, ФНЧ и спектроанализатор, при этом выход первого генератора гармонических сигналов соединен с первым входом аналогового сумматора и первым входом мультиплексора, выход второго генератора гармонических сигналов соединен с вторым входом аналогового сумматора и третьим входом мультиплексора, выход аналогового сумматора соединен со вторым входом мультиплексора, выход которого подключен к входу АЦП, выход которого подключен к входу демультиплексора, первый выход которого соединен с входом первого элемента задержки, второй выход с вторым входом вычитающего устройства, первый вход которого подключен к выходом первого элемента задержки, а второй вход - с выходом второго элемента задержки, а второй вход - с выходом второго элемента задержки, а второй вход - с выходом второго элемента задержки, а второй вход - с выходом второго элемента задержки, а второй вход - с выходом второго элемента задержки [2].

Недостатком известного устройства является пониженная полоса рабочих частот при измерении нелинейности АЦП, вследствие: во-первых, влияния частотных характеристик ЦАП на результаты измерения; во-вторых, ограничения частотного диапазона за счет использования в известном измерителе синхронно-управляемых устройств выборки и хранения, к быстродействию которых предъявляются, жесткие требования; в-третьих, уменьшения максимальной частоты дискретизации используемого АЦП в 3 раза, из-за трехтактного режима работы известного устройства, при котором лишь в каждом третьем такте производится измерение нелинейных искажений преобразователя.

В основу изобретения поставлена задача создания такого измерителя нелинейности АЦП, в котором введение новых блоков позволило бы обеспечить расширение частотного диапазона измерения.

Поставленная задача решается тем, что в измеритель, содержащий первый и второй генераторы гармонических сигналов, аналоговый сумматор, испытуемый аналого-цифровой преобразователь, последовательно включенные цифроаналоговый преобразователь, фильтр нижних частот и анализатор спектра, при этом выход первого генератора гармонических сигналов соединен с первым входом аналогового сумматора, выход второго генератора гармонических сигналов соединен с вторым входом аналогового сумматора, выход которого подключен к аналоговому входу испытуемого аналого-цифрового преобразователя, введены буферный накопитель, генератор импульсов, элемент И, делитель частоты, первый триггер, мультиплексор, второй триггер, счетчик адреса, шина сброса и шина запуска, которая объединена с S-входом первого триггера, R-входом второго триггера и R-входом счетчика адреса, разрядные выходы которого подключены к соответствующим адресным входам буферного накопителя, а выход переполнения соединен с S-входом второго триггера, выход которого объединен с управляющим входом мультиплексора и входом записи-считывания буферного накопителя, входы данных которого подключены к соответствующим цифровым выходам испытуемого аналого-цифрового преобразователя, а выходы данных к соответствующим цифровым входам цифроаналогового преобразователя, при этом выход генератора импульсов соединен с первым входом элемента И, а выход первого триггера с вторым входом элемента И, выход которого объединен с вторым информационным входом мультиплексора и входом делителя частоты, выход которого подключен к первому информационному входу мультиплексора, выход которого объединен с С-входом счетчика и С-входом синхронизации испытуемого аналого-цифрового преобразователя, при этом шина сброса подключена к R-входу первого триггера.

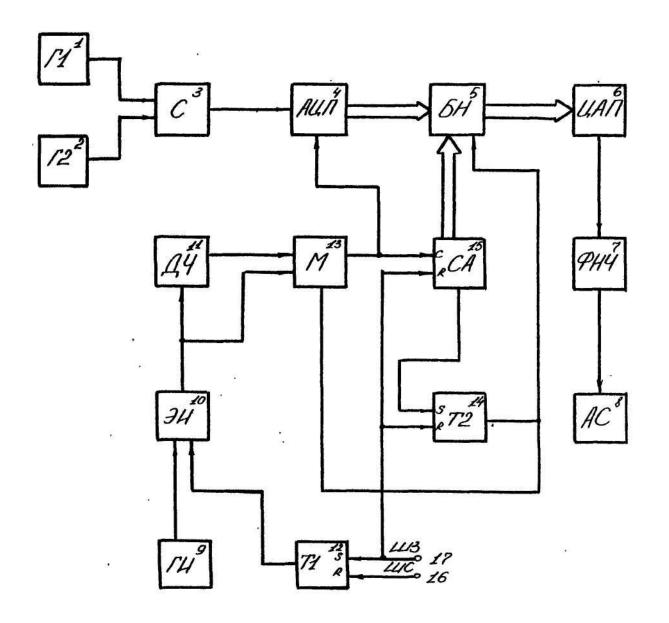

На чертеже представлена функциональная схема измерителя нелинейности АЦП.

Измеритель содержит первый 1 и второй 2 генераторы гармонических сигналов (Г1 и Г2), аналоговый сумматор (С) 3. испытуемый АЦП 4, буферный накопитель (БН) 5, ЦАП б, ФНЧ 7, АС 8, генератор импульсов (ГИ) 9, элемент И (ЭИ) 10, делитель частоты (ДЧ) 11; первый триггер (Т1) 12, мультиплексор (М) 13, второй триггер (Т2) 14, счетчик адреса (СА) 15, шина сброса (ШС) 16, шина запуска (ШЗ) 17.

Первый вход аналогового сумматора 3 соединен с выходом первого генератора гармонических сигналов 1, второй вход - с выходом второго генератора гармонических сигналов 2, а выход - с аналоговым входом испытуемого аналого-цифрового преобразователя 4. Входы данных буферного накопителя 5 соединены с соответствующими цифровыми выходами испытуемого АЦП 4, выходы данных - с соответствующими цифровыми входами ЦАП 6, адресные входы - с соответствующими разрядными выходами счетчика адреса 15, вход записи-считывания объединен с выходом второго триггера 14, и управляющим входом мультиплексора 13. С-вход счетчика адреса 15 объединен с С-входом испытуемого АЦП 4 и выходом мультиплексора 13. Выход делителя частоты 11 соединен с первым информационным входом мультиплексора 13, а вход - объединен с выходом элемента И 10 и вторым информационным входом мультиплексора 13. Первый вход элемента И 10 подключен к выходу генератора импульсов 9, а второй -к выходу первого триггера 12, R-вход которого соединен с шиной сброса 16, а S-вход объединен с шиной запуска 17, R-входом второго триггера 14, R-входом счетчика адреса 15, выход переполнения которого соединен с S-входом второго триггера 14. Вход ФНЧ 7 соединен с выходом ЦАП 6. а выход - с входом анализатора спектра 8.

Устройство работает следующим образом.

С помощью генераторов 1 и 2 гармонических сигналов и аналогового сумматора 3 на выходе последнего

формируется двухтональный сигнал, который поступает на вход испытуемого АЦП 4. При воздействии двухтонального тестового сигнала вследствие нелинейности передаточной характеристики АЦП в спектре выходного преобразованного сигнала содержатся, кроме составляющих основных частот дополнительные составляющие на комбинационных и гармонических частотах. Выходной цифровой сигнал АЦП поступает на входы данных буферного накопителя 5, который работает в двух режимах: записи и считывания. Выход режима осуществляется выходным сигналом второго триггера 14 по входу запись-считывания буферного накопителя. При появлении на шине запуска 17 одиночного импульса на выходе триггера 14 устанавливается уровень логического "0", который задает для буферного накопителя режим записи данных и выбирает импульсы с частотой F₁ с выхода элемента И 10 через мультиплексор 13. Кроме того, запускающий импульсный сигнал на шине 17 устанавливает счетчик адреса 15 в нулевого состояние, а триггер 12 - в единичное. Наличие логической "1" на входе элемента И 10 разрешает прохождение тактовых импульсов с частотой F₁ с выхода генератора импульсов 9 на вход делителя частоты и на второй информационный вход мультиплексора. Импульсы с частотой F<sub>1</sub> подводятся на счетный вход счетчика адреса 15, который формирует на своих разрядных выходах монотонно-возрастающий код, поступающий на адресные входы БН, Эти же импульсы являются стробирующими для испытуемого АЦП. Таким образом, переключением адресных сигналов с частотой  $F_1$  производится запись цифровых - кодов АЦП в ячейки памяти БН. После полного накопления буферного запоминающего устройства на выходе переполнения счетчика адреса появляется импульс, переводящий второй триггер в единичное состояние, который устанавливает на входе записьсчитывания БН режим считывания данных. Логическая "1", поступающая с выхода триггера 14 на управляющий вход мультиплексора 13, разрешает прохождение импульсов с частотой F2 на счетчик адреса. В режиме считывания вход данных БН не воспринимает информацию с выхода АЦП. Перебором адреса с частотой F2 производится выдача накопленных цифровых кодов АЦП с выхода данных БН на вход ЦАП 6, которые преобразуются в аналоговый сигнал и через ФНЧ 7 подается для дальнейшей оценки на вход анализатора спектра 8. Процесс считывания данных с выхода БН прекращается после появления одиночного импульса на шине сброса 16, который переводит триггер 12 в нулевое состояние, запрещает прохождение импульсов от ГИ 9 и останавливает счет СА 15. Частота F<sub>1</sub> равна максимальной частоте дискретизации испытуемого АЦП 4. Частота F2 определяется быстродействием ЦАП 6 и обычно выбирается из соотношения F<sub>2</sub> ≤ 0,1 F<sub>1</sub>. Это обеспечивает высокую частоту дискретизации АЦП и пониженную скорость преобразования в ЦАП выходных цифровых кодов БН 5. Таким образом, в заявляемом устройстве исключается принципиальное ограничение ширины полосы частот измерения, характерное для всех визуальных методов контроля нелинейности АЦП, при которых быстродействие ЦАП должно было на порядок превышать максимальную частоту дискретизации ЦАП. При этом существенно увеличивается частотный диапазон измерения без использования в устройстве сверхбыстродействующих ЦАП.