### МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАІНИ

ОДЕСЬКА НАЦІОНАЛЬНА АКАДЕМІЯ ХАРЧОВИХ ТЕХНОЛОГІЙ

# ХІ МІЖНАРОДНА НАУКОВО-ПРАКТИЧНА КОНФЕРЕНЦІЯ

# ІНФОРМАЦІЙНІ ТЕХНОЛОГІЇ І АВТОМАТИЗАЦІЯ – 2018

Збірник доповідей

Частина І

Одеса, 4-5 жовтня 2018

### **3MICT**

| PUTILINA DARIA, MEDVEDEV MAXYM, TROYNINA ANASTASYA        | 3  |

|-----------------------------------------------------------|----|

| VYATKIN SERGEY I., ROMANYK ALEXANDER N.                   | 5  |

| VYATKIN S.I., ROMANYUK S.A., PAVLOV S.V.                  | 8  |

| KRASILENKO V.G., LAZAREV A.A., NIKITOVICH D.V.            | 12 |

| ВОЛКОВ В.Э., КОВАЛЕНКО А.В., МАКСИМОВА О.Б.               | 19 |

| LOBODA U.G., KIRICHENKO V.I., VOLKOV V.E.                 | 20 |

| VOLKOV V.E., MAKOYED N.A.                                 | 22 |

| ГАБУЕВ К.О., ЕГОРОВ В.Б.                                  | 24 |

| ГОНЧАР В.О.                                               | 27 |

| ГРАТІЙ Т.І., БЕРЕЗОВСЬКА Л.В.                             | 28 |

| ДУБОВКА В. С.                                             | 30 |

| ZHYGAILO A.M., DETS D.V.                                  | 32 |

| ІВАНОВА Л.В., КРАСНІЄНКО Н.В.                             | 35 |

| КОВАЛЕВСЬКИЙ В. М.                                        | 37 |

| КОВАЛЬЧУК Д. А., МАЗУР О.В.                               | 40 |

| ЖУЧЕНКО О. А., КОРОТИНСЬКИЙ А. П.                         | 43 |

| КОТЛИК С.В., КОРНІЄНКО Ю.К., СОКОЛОВА О.П., ПАРФЕНЮК О.Є. | 45 |

| КОТЛИК С.В., СІРОМЛЯ С.Г., КУПРІЯНОВ А.Б.                 | 48 |

| KRYVCHENKO Yu., KRYVCHENKO A.                             | 50 |

| LEVINSKYI V.M., LEVINSKYI M.V.                            | 52 |

| МАЗУРОК Т.Л.                                              | 53 |

|                                                           |    |

#### KRASILENKO V.G., LAZAREV A.A., NIKITOVICH D.V. VNTU (Ukraine)

# DESIGN AND SIMULATION OF CONTINUOUSLY LOGICAL ANALOG-TO-DIGITAL CONVERTERS WITH ADCANCED FUNCTIONS FOR IMAGE PROCESSORS

Abstract. The paper considers results of design and modeling of continuously logical analog-todigital converters (CL\_ADC) based on current mirrors (CM) with advanced functions of preliminary analogue and subsequent processing for creating sensor multi-channel analog-to-digital converters (SMC ADCs) and image processors (IP). For such with parallel inputs-outputs IP and SMC ADCs it is needed active photosensitive basic cells (BC) with an extended electronic circuit, which are considered in paper. Such BCs and ADCs based on them have a number of advantages: high speed and reliability, simplicity, small power consumption, high integration level for linear and matrix structures. We show design of the BC and CL\_ADC of photocurrents and their possible implementations and its simulations. We consider CL\_ADC with conversion to binary codes and Gray codes. Each channel of the structure consists of several digital-analog cells (DC) on 15-35 CMOS. The amount of DC does not exceed the number of digits of the formed code, and for an iteration type, only one cell of DC, complemented by the device of selection and holding (SHD), is required. One channel of CL ADC with iteration is based on one DC-(G) and SHD, and it has only 35 CMOS transistors. In such ADCs easily parallel code can be realized and also serial-parallel output code. The circuits and simulation results of their design with OrCAD are shown. The supply voltage of the DC is  $1.8 \div 3.3V$ , the range of an input photocurrent is  $0.1 \div 24 \mu A$ , the transformation time is  $20 \div 30 nS$  at 6-8 bit binary or Gray codes. The general power consumption of the ADC with iteration is only  $50\div100\mu W$ , if the maximum input current is  $4\mu A$ . Such simple structure of linear array of ADCs with low power consumption and supply voltage 3.3V, and at the same time with good dynamic characteristics (frequency of digitization even for 1.5µm CMOS-technologies is 40÷50 MHz, and can be increased up to 10 times) and accuracy characteristics are show. The CL\_ADCs opens new prospects for realization of photo-electronic structures and IP with matrix operands, which are necessary for neural networks, digital processors fuzzy controllers.

Introduction. Too slow and too few interconnects between VLSI circuits cause a bottleneck in the communication between processor and memory or processors. The problem is getting worse since the increasing integration density of devices leads to a higher requirement in the number of necessary channels for the off-chip communication. The use of optical interconnects is discussed as an alternative to solve the mentioned problems on interconnect in VLSI technology. A lot of demonstrator systems were built to prove the use of optics or optoelectronics for off-chip and on-chip interconnects. In OE-VLSI one tries to solve limitation problem by realizing external interconnects not at the edge of a chip but with arrays of optical detectors and light emitters which send and receive data directly out from the chip area. This allows the realization of stacked 3-D chip architecture in principle [1]. At present the situation for smart detector circuits is much easier. They can be regarded as a subset of OE-VLSI circuits because they consist only of arrays of photo-detectors with corresponding evaluation circuit for analogue to digital converting. Optical detectors based on photodiodes can be monolithically integrated with digital electronics in silicon, which significantly simplifies design of OE-VLSI circuits, which in addition should contain only light-emitting devices. Furthermore smart detector circuits can be manufactured in nearly every semiconductor fabric. Smart optical sensors [2, 3] show a great application field and market potential. Therefore our approach favors smart pixel like architecture combining parallel signal detection with parallel signal processing in one circuit. Each pixel has its own analog and analog-digit node what guarantees the fastest processing. The strategic direction of solution of various scientific problems becomes fast-acting and parallel processing of 2D data large arrays using non-conventional computational MIMOsystems, corresponding matrix logics (ML) (multi-valued, signed-digit, fuzzy logics, continuous, neuralfuzzy and others) and corresponding mathematical apparatus [4-7]. For realizations of optical learning neural networks (NN) with 2D structure [4, 8-10], of the continuous logic equivalency models (CLEM) NN [5, 8, 9], the elements of matrix logic are required, and not only of two-valued, but also continuous, threshold logics [5-7]. The adequate structure of vector-matrix computational procedures with basic operations of above-mentioned logics, are required. Advanced non-traditional parallel computing structures

and MIMO-systems [3], require both parallel processing and parallel inputs/outputs. In article [11] mathematical foundations of the universal (multifunctional) logic elements (ULE) of the ML design with fast programmable tuning are considered, where the expediency of functional basis unification and the need for ADC [12] arrays and storage (matrix type) has been shown. ADC is continuously-discrete automaton, which is carrying out transformation of analogue size x by its interaction with standard in sizes in a discrete output code. Aspects of the theory and designing practice and use ADC and DAC are so widely stated, what even it is difficult to choose the most generalizing works. Certain successes are attained in area of creation of 2D devices of ML, 2D storages for such parallel informatively-measuring systems and digital optoelectronic processors (DOEPs). "Bottleneck" in parallel DOEP is ADC, which unlike traditional systems of input with scanning or series-parallel reading and output, should make in parallel completely ADC considerable quantity transformation (256 x 256 and more) signals and to provide rate of input, up to 10<sup>6</sup>-10<sup>7</sup> frames per second. Therefore only creation SMC ADC images with multi parallel inputs and outputs, i.e. ADC with vector or matrix organization (VMO) [12-14], which all channels work in parallel and provide (low power consumption, simple circuit realization, small time of transformation, low levels of the entrance signals, comprehensible word length and i.e.), the abovestated problems can solve. Besides, such ADC VMO also can carry out and other functions, for example, calculation of logic operations over matrixes, a digital filtration and digital addition-subtraction of images. In papers [13, 14] equivalently (EQ) continuously logical (CL) ADC which allows to obtaining high performance with smaller amounts of equipment were considered. Such ADC consist of n serially connected digital-analog cells (DCs), implementing CL - functions and built in CMOS-transistors with a current-mode operation. The selection of the required continuously-logical functions for analog-to-digital conversion and corresponding ABC circuits influences on parameters and performance of such CL ADC, including the output codes. An amount of channels in multichannel converters for the optical parallel and multisensory systems is considerable. Formulation of the problem and goal of the work. Therefore for such applications digit-by-digit serial-parallel arrays are more preferable. Consequently, the aim of our work is design and modeling ADC and their of CL DCs based on CM with functions of preliminary analogue and subsequent analogue-digital processing for creating sensor multi-channel analog-to-digital converters (SMC ADCs) and image processors (IP). In addition, in our previous works, the accuracy characteristics of the ADC were not considered, no estimates of conversion errors were made for different possible modes and modifications of such CL DCs and ADCs as a whole. That is why the purpose of the present work is also to evaluate ADC errors, demonstrate them by specific experimental results, and also further enhancements of such ADCs and their basic cells, which significantly expand their functionality and the range of problems they solve.

#### Research results. 1. Basic foundations, equivalence models for SMC\_CL\_ADC.

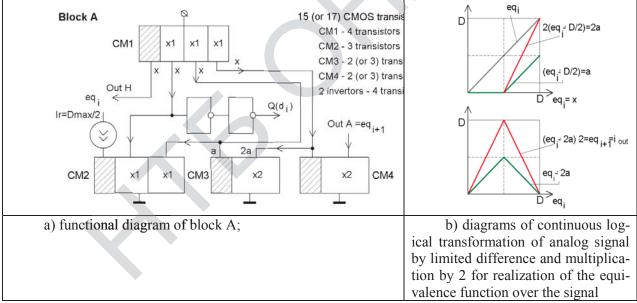

The CL – transformations are shown in papers [13], in which the transformation CL functions (CLF) are defined and it is shown that the operation of min, max of CL are the basic operations of the  $D_1[P(x1,x2)] = max(x_1,x_2)$ functions. Use of operators of hybrid logic it is possible:  $D_2[P(x1,x2)] = min(x_1,x_2)$ , where P and D are respectively the threshold and the de-threshold operators, which are realized by various means. In many NN models for recognition of images, especially a lot of graded, it is desirable to have picture binary bit-planes, which encode the image matrix in Gray codes. Besides, in a number of works [5-9] it has been shown that some operations of continuous logic, such as equivalence and nonequivalence, and their generalized family. These scalar operations of equivalence eq(x,y) and nonequivalence neq(x,y) for x,y  $\in [0,1]$  are defined in works [5, 13, 14] namely: eq (x, y) =  $_{X}\Lambda y + \bar{x}\Lambda\bar{y} = \min(x, y) + \min((1-x), (1-y)) = 1 - |x-y|,$ neq(x,y)=  $|x-y| = 1 - eq(x,y) = \max(x,y) - \min(x,y) = \max(\bar{x},\bar{y}) - \min(\bar{x},\bar{y}) = (x - y) + (y - x),$ where  $(\dot{-})$  - is the operation of a limited difference. If we consider that at  $y = 1 \dot{-} x = \bar{x}$ , these functions are transformed to:  $eq(x, \overline{x}) = 2(x \land \overline{x}) = 2min(x, \overline{x}), \quad neq(x, \overline{x}) = max(x, \overline{x}) - min(x, \overline{x}) = 1$  $2\min(x, \overline{x})$ , as has been shown in works [13], these functions can be successfully used in CL ADC. For formation of binary bit-planes which answer picture categories of a Gray code, we used per pixel iterative procedure over matrixes of equivalence and nonequivalence of signals or equivalence and nonequivalence, received on the previous steps:  $eq_{i+1}(eq_i(...), neq_i(...))$  and  $neq_{i+1}(eq_i(...), neq_i(...))$ . It is easy to notice that splitting of a piece [0, 1] on  $2^n = N$  sub-bands, puts to each of them a set, a vector of signs which corresponds to a code Gray, the measured scalar size x. Thus, positional digit  $d_{n-i}$  of code is de-

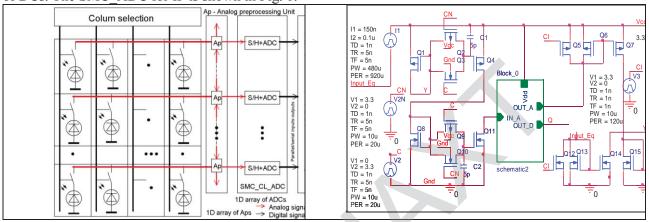

fined  $d_{n-i}(eq_{i-1}, neq_{i-1}) = \{1, if eq_{i-1} > neq_{i-1}, 0, if else\}$  where  $i \in 1 \div n$ ,  $eq_0 = x$ ,  $neq_0 = \bar{x}$ . From here evidently, that for realization ADC of optical signals, we needed to synthesize the CL BCs, which realize demanded operations eqi, neqi and the threshold operators. We name such ADC equivalently continuous-logic complementary-dual, as in them signals x and  $\overline{x}$  are complementary and functions CL are equivalence (nonequivalence), i.e. equivalently CL ADC [13]. Since these ADC were implemented on the current mirrors (CM), and input signals of ADC are currents, then we shall denote such ADC as ADC this work as transformation CLFs we use the following CM. In functions:  $eq_{i+1}(eq_i, D/2) = 2(eq_i - 2(eq_i - D/2))_{OT} neq_{i+1}(neq_i, D/2) = 2|neq_i - D/2|, where eq_0 = x, neq_0 = \bar{x}$ , which allow us to work not with two signals, but with 1 signal, thereby simplifying the implementation of DCs. The SMC ADC for IP is shown in Fig. 1

Fig. 1. Structure of 2D image sensor with 1D array of CL\_ADC and storage or/and digital codes processing unit (left). Functional diagram of CL\_ADC CM-6(8) (G) -iv) (right).

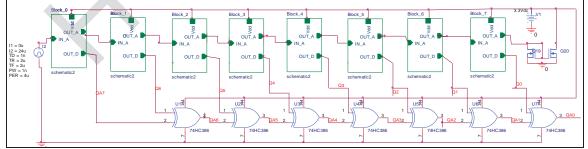

Fig. 2. Circuits of the one channel of multichannel CL\_ADC CM-6(8) (G) -iv with iteration transformation and base cell DC-(G)

# 2. Design of CL ADC CM-6(8) (G) -iv (the iteration variant) on DC-(G) (with Gray code) with Orcad.

Circuit of the one channel of SMC\_ADC is shown in Fig.1. The circuit is based on one digitalanalog cells DC-(G) (Block A), devices of selection and holding (SHD) and additional elements (Block B). The block A or (DC) is shown in Fig. 2a. Essence of the circuit is in that input analog current signal, subject to transformation, is written to SHD, and than given to analog DC-(G), which will form the next digital bit of output code and CL function which in future will be again given on SHD for forming next successive bits. DC - (G) consists of 15 or 17 transistors (Ts) and current generator. Device of SHD is based on 18 transistors. Thus complication of the circuit of one channel is 33 (35) transistors, which do it perspective for wireless multisensory systems. The DC converts the input signal to another output current signal, using CLF (section 1) over currents and simultaneously compares it with the threshold current. Thus, there is a wide choice for searching and optimizing such DCs taking into account the required goal. To minimize the hardware costs, cells can be very simple and consist of 10-20 Ts. The advantage of a structure with a serial output of the Gray code is that increasing the number of iterations increases the bit ADC with an unchanged structure. To convert a serial Gray code to a binary code, only one modulo adder and one D flip-flop are required. In Figures 3 the results of simulation of one channel of six bits CL\_ADC CM-6 (G) -iv) at linear-increasing input currents are shown. The total power consumption of this ADC-6 (8) (G) -iv did not exceed 70 $\mu$ W with a maximum input current of 4  $\mu$ A and a conversion period of 120 $\mu$ S (6x20  $\mu$ S for 6 bits) and 160 $\mu$ S (8x20  $\mu$ S for 8 bits). For modes with lower currents and Vdd = 1.5 ÷ 1.8V, the power consumption of ADC-6 (8) can be reduced to 10 ÷ 15 $\mu$ W.

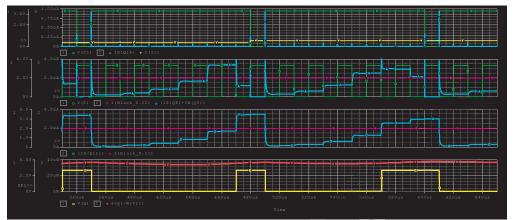

Fig. 3. a) Simulation result for two input currents 100nA and 150nA, corresponding output Gray codes {000001} and {000011}; the blue line in the third trace is output current of the block for six digits ADC, the violet line is the threshold current; the yellow line in the fourth trace is output voltage of the block that corresponds to output code (a time interval for the first code 370 $\mu$ s - 490  $\mu$ s (six digits by 20  $\mu$ s), a time interval for the second code 490 $\mu$ s - 610  $\mu$ s; the red line is the consumption power about 40 $\mu$ W

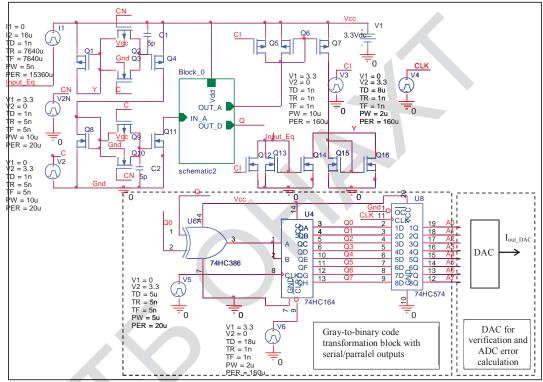

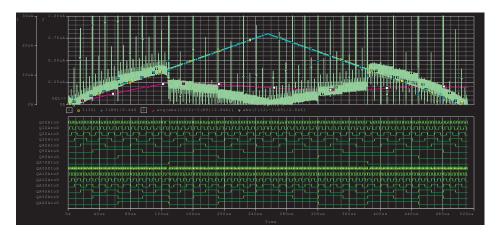

The simulation results and diagrams, under other modes and currents, will be presented in the report. They confirm the correct functioning of the proposed ADC. The drawback of our earlier works is the lack of research on the ultimate capabilities of such structures and their precision characteristics. Therefore, in this paper, we pre-observed such a structure in the formation of eight digit code, determined the possibility of operation with very small input currents (10nA  $\div$  1µA), and adding to the structure of the DAC and converters from the Gray code to the binary code (see Fig. 4 and Fig. 5 with parallel outputs), determined the magnitude of ADC errors and its accuracy characteristics. At the decline of requirements to the fast-acting the offered chart allows using the analog-digital transformations for less amplitude input currents and, power consumption of such one channel of ADC can be less than 50µW for Dmax=1µA. All shown circuits are simulated on 1.5 µm CMOS Ts. Analog-to-digital conversion errors simulation is shown in Fig. 6. The simulation is done for Dmax= $4\mu$ A, 6-bit ADC, conversion period T=120 µs. As shown in the Fig. 6 the maximal error is about 1 least significant bit (LSB), and only for maximal input current is about 2 LSB for 8-bit ADC. In Fig. 4 diagram of CL ADC CM-(8) (G) - iv with Gray-to-binary code transformation and serial/parallel outputs with code converter and DAC for errors calculation are shown. Actually the ADC itself, from which 1D or 2D arrays will be done for sensors or image processors, in contrast to the circuit in Fig. 2 may additionally comprise some digital elements, for example, a logic element and a trigger or register. This depends on the possible modes and requirements regarding the formats of output and storage of code arrays. Therefore, in Fig. 4, these additional optional units are marked with a dash-dotted line. And to test the accuracy and timing characteristics in the dynamics, we used two registers and DAC. The results of modeling this circuit are partially shown in Fig. 6 and confirm the correct operation and analog-to-digital and code conversion, both when linearly increasing (decreasing) and sinusoidal current signals are applied to the ADC input. They show that for the 8-bit ADC, even in high-speed (Imax to  $16 \div 24\mu A$ ) and low-voltage lowfrequency energy-efficient modes (with Imax, namely 1µA, 4µA), the maximum error does not exceed 4  $\div$  5 quantization quanta, and the average error does not exceed 2 LSB. The simulations results CL ADC with a parallel-serial output have shown, that in such parallel-conveyor CL ADC (P C) 6 (8)-DC-(G) at change Imax from 16µA to 24µA the consumption power at 3,3 V was from 1µW to 2µW(6 bits) and  $3\mu$ W(8 bits). The conversion frequencies in the experiments were for these currents: 32, 40, 50 MHz for 16µA and 64 MHz for 24µA and 40µA. They correspond to different regimes: different Imax, namely 1µA, 4µA, 16µA, 24µA, 40µA; various 1,5V, 1,8V, 2,5V, 3,3V; various transformation periods T (0,02µS, 0,025µS, 1µS, 20µS, 100µS) etc. These researches show, that power consumption actually ADC for the specified values Imax (equal 1µA and 1,8V, 64nA and 1,5V) makes accordingly 40µW and 2µW, tht quantization step is 15,625nA for Imax=4µA and 62.5nA for Imax=16µA, and quantization frequency 40 MHz.

**Conclusions.** Thus we offered variants of realization of digital-analog cells (DC) and structures of CL ADC CM on their basis. It is shown that such ADC have simplicity, because the amount of DCs does not exceed the number of digits of the formed code, and for an iteration type, only one DC, complemented by the device of selection and holding, is required. In such ADC easily parallel code can be realized and also serial-parallel output code. The circuits and simulation results of their design with OrCAD are shown.

Fig. 4. Functional diagram of CL\_ADC CM-(8) (G) -iv) with Gray-to-binary code transformation and serial/parallel outputs with code converter and DAC for errors calculation.

Fig. 5. Structure of 8 bit ADC: a) with Gray code parallel outputs (Q0-Q7); b) with Gray-to-binary code transformation and parallel outputs (QA0-QA7)

Fig. 6. Time diagrams of 8 bit parallel CL\_ADC signals by simulation for  $I_{input_max}=24\mu A$ , ADC conversion time is 1 $\mu$ s; the blue line is the DAC output current, the yellow line is the ADC input current, the violet line is the average ADC current error (<250nA), the green line is the ADC current error; QA0-QA7 – output digital signals of binary parallel code, Q0..Q7 (Q7=QA7) – output digital signals of Gray parallel code

**Conclusions** (continuation). Such simple CL\_ADC CM with low power consumption  $\leq 3$ mW and supply voltage 1.8÷3.3V, and at the same time with good dynamic characteristics (frequency of digitization even for 1,5µm CMOS-technologies is 40MHz, and can be increased up to 10 times) and accuracy ( $\Delta$  quantization=15.6÷62.5nA for Imax=4÷16µA) characteristics are shown. The range of optical signals, taking into account sensitivity of modern photo-detectors, can be 1-200 µW. One channel of the ADC with iteration is based on one DC-(G) and SHD, and it has only 35÷40 CMOS transistors. Since such 1D, 2D arrays of serial ADCs are very perspective for sensors and IP. The general power consumption of one ADC, in this case, is only 50÷70µW, if the maximum input current is 4µA. For high performance and frequency of conversions, it is preferable to use the parallel-pipeline CL\_ADC (P\_C) scheme based on the set of 8-DC-(G) with parallel-serial outputs. The maximal error is about 1 LSB, and only for maximal input current is about 2 LSB for 8-bit CL\_ADC.

#### References

- Lei Yi, Guangbao Shan, Song Liu, Chengmin Xie, High-performance processor design based on 3D on-chip cache, Microprocessors and Microsystems, Volume 47, 2016, Pages 486-490, ISSN 0141-9331, http://dx.doi.org/10.1016/j.micpro.2016.07.009.

- Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., "Multichannel serial-parallel analog-todigital converters based on current mirrors for multi-sensor systems", Proc. SPIE Vol. 8550, Optical Systems Design 2012, 855022 (January 3, 2013); doi:10.1117/12.2001703.

- Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., "Designing and simulation smart multifunctional continuous logic device as a basic cell of advanced high-performance sensor systems with MIMO-structure", in Photonics, Devices, and Systems VI, Dagmar Senderáková; Petr Páta; Pavel Tománek, Editors, Proceedings of SPIE Vol. 9450 (SPIE, Bellingham, WA 2015), 94500N

- 4. Mori, M., Yatagai, T., "Optical learning neural networks with two dimensional structures," Proc. SPIE 3402, 226-232 (1997).

- Krasilenko, V., Nikolskyy, A., Zaitsev A., Voloshin V., "Optical pattern recognition algorithms on neural-logic equivalent models and demonstration of their prospects and possible implementations," Proc. SPIE 4387, 247 –260 (2001).

- Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A. [Design and Simulation of Time-Pulse Coded Optoelectronic Neural Elements and Devices, Optoelectronic Devices and Properties], In-Tech (2011). ISBN: 978-953-307-204-3, DOI: 10.5772/16175. Available from: <u>http://www.intechopen.com/books/optoelectronic-devices-andproperties/design-and-simulationof-time-pulse-coded-optoelectronic-neural-elements-and-devices</u>

- Krasilenko, V., Ogorodnik, K., Nikolskyy, A., Dubchak, V., "Family of optoelectronic photocurrent reconfigurable universal (or multifunctional) logical elements (OPR ULE) on the basis of continuous logic operations (CLO) and current mirrors (CM), "Proc. SPIE 8001, (2011).

- 8. Krasilenko, V. G., Lazarev, A., Grabovlyak, S., "Design and simulation of a multiport neural

network heteroassociative memory for optical pattern recognitions," Proc. of SPIE Vol. 8398, 83980N-1 (2012).

- Krasilenko V. G., Alexander A. Lazarev, Diana V. Nikitovich, "Experimental research of methods for clustering and selecting image fragments using spatial invariant equivalent models," Proceedings of SPIE Vol. 9286, 928650 (2014).

- Krasilenko V.G., Lazarev A.A., Nikitovich D.V., "Modeling and possible implementation of self-learning equivalence-convolutional neural structures for auto-encoding-decoding and clusterization of images," Proceedings of SPIE Vol. 10453, 104532N (2017)

- Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., "Simulation of reconfigurable multifunctional continuous logic devices as advanced components of the next generation highperformance MIMO-systems for the processing and interconnection", Proceedings of SPIE Vol. 9009, 90090R (2014).

- 12. Kolesnitsky, O. K., Krasilenko, V. G., "Analog-to-digital converters with picture organization for digital optoelectronic processors", Autometric, 2, 16-29 (1992).

- Krasilenko, V. G., Nikolskyy, A. I., Krasilenko, O. V., Nikolska, M. A., "Continuously logical complementary dual equivalently analog-to-digital converters for the optical systems," Proc. SPIE 8001-30, (2011).

- Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., Krasilenko, O. V., Krasilenko, I. A., "Simulation of continuously logical ADC (CL ADC) of photocurrents as a basic cell of image processor and multichannel optical sensor systems", Proceedings of SPIE Vol. 8774, 877414 (2013).

#### ХІ МІЖНАРОДНА НАУКОВО-ПРАКТИЧНА КОНФЕРЕНЦІЯ

### ІНФОРМАЦІЙНІ ТЕХНОЛОГІЇ І АВТОМАТИЗАЦІЯ – 2018

ОДЕСА 4 – 5 ЖОВТНЯ, 2018

Збірник включає доповіді учасників XI Міжнародної науково-практичної конференції «Інформаційні технології і автоматизація – 2018»

Редакційна колегія: Котлик С.В., Хобін В.А.

Комп'ютерний набір і верстка: Шамрай О.А.

Відповідальний за випуск: Котлик С.В.

### ДЛЯ НОТАТОК