## RÉPUBLIQUE FRANÇAISE

## INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

(1) N° de publication : (A n'utiliser que pour les commandes de reproduction). 2 500 971

**PARIS**

A1

## DEMANDE DE BREVET D'INVENTION

<sub>20</sub> N° 81 04127

- - [72] Invention de : Alexei Petrovich Stakhov, Alexei Dmitrievich Azarov et Vladimir Andreevich Luzhetsky.

- 73 Titulaire : Idem 71

- Mandataire : Cabinet Plasseraud, 84, rue d'Amsterdam, 75009 Paris.

Convertisseur analogique-numérique.

La présente invention concerne les appareils de calcul et de mesure numériques et plus particulièrement les convertisseurs analogiques-numériques.

Le convertisseur faisant l'objet de l'invention 5 peut être utilisé avec intérêt par exemple pour la mesure de grandeurs électriques. Par ailleurs, il peut être employé dans des systèmes automatisés et automatiques de commande et de régulation pour assurer la liaison entre un objet et son moyen de commande.

Les instruments de mesure auxquels se rapporte plus particulièrement le convertisseur faisant l'objet de l'invention sont à soumettre au contrôle métrologique, c'est-à-dire à des vérifications concernant la conformité de leurs caractéristiques métrologiques aux grandeurs requises.

Pour réaliser de tels contrôles, on doit disposer d'un large jeu d'étalons difficile à obtenir au point de vue technique tandis que le processus luimême de contrôle métrologique demande beaucoup de 20 temps.

On connaît par exemple un convertisseur analogique-digital (Azarov A.D. "Analogo-tsifrovoi preobrazovatel s tsiklicheskim utochnenieum rezultats. Pribory i tekhnika experimenta", 1979, N° 2, p. 96-97) comprenant (K-1) amplificateurs, (K-1) convertisseurs numériques-analogiques et un comparateur à seuils multiples. Le convertisseur connu comporte en outre un traducteur de code parallèle, un commutateur analogique, un additionneur, un registre et une unité de commande. La première entrée du premier amplificateur est reliée à la première entrée du commutateur analogique et constitue l'entrée du convertisseur analogique-numérique. La sortie de l'i-ème convertisseur numérique-analogique est reliée à la seconde entrée de l'i-ème amplificateur

dont la première entrée est couplée à la sortie de l'(i-l)-ème amplificateur. La sortie de chacun des (K-1) amplificateurs est connectée à l'entrée correspondante (depuis la deuxième à la K-ème) du commuta-5 teur analogique. La seconde sortie de ce dernier est connectée à l'entrée de l'unité de commande, sa première sortie est reliée à l'entrée du comparateur à seuils multiples. La première sortie de celui-ci est couplée à l'entrée du traducteur de code parallèle 10 dont la sortie est associée à l'additionneur. La sortie de l'additionneur est couplée à l'entrée du registre et elle constitue la sortie du convertisseur analogiquenumérique. Les entrées de l'i-ème convertisseur numérique-analogique sont reliées aux sorties correspondantes 15 du registre, les entrées de commande du commutateur analogique et du comparateur à seuils multiples sont couplées aux sorties correspondantes de l'unité de commande.

La conversion d'une grandeur analogique en code 20 binaire à  $\underline{n}$  bits (unités binaires) s'opère en  $\underline{k}$  cycles dont chacun voit se former  $\underline{m}$  bits du code.

Les éléments participant à l'i-ème cycle sont :

(i-l) amplificateurs, (i-l) convertisseurs numériquesanalogiques, i-ème canal du commutateur analogique et

unités restantes du convertisseur analogique-numérique

connu.

Au cours du premier cycle, la grandeur analogique prélevée sur l'entrée du convertisseur connu est appliquée à la première entrée du commutateur analogique,

30 lequel, sous l'action d'un signal de commande provenant de l'unité de commande, transmet ladite grandeur à l'entrée du comparateur à seuils multiples. Ledit comparateur traduit la grandeur analogique d'entrée en un code unitaire parallèle qui à son tour est converti,

35 au moyen du traducteur de code parallèle en un code binaire à position. Le code ainsi obtenu est ajouté

4

25

au contenu de l'additionneur. Le résultat de l'addition est enregistré au registre mémoire. Le code en provenance du registre est traduit par le convertisseur numérique-analogique en une grandeur analogique 5 qui est appliquée à la seconde entrée du premier amplificateur. La différence des grandeurs analogiques arrivant aux entrées de l'amplificateur est envoyée, après amplification, à la seconde entrée du commutateur. Ensuite, le processus de conversion est répété 10 de façon analogue.

Le contrôle métrologique d'un tel convertisseur présente un caractère compliqué. Ce convertisseur se distingue, d'autre part, par une fiabilité basse qui ne permet pas d'obtenir la valeur réelle de l'équiva-15 lent numérique de la grandeur analogique d'entrée en cas de défaillance, ne serait-ce que d'un seul des bits du convertisseur numérique-analogique.

L'invention vise à mettre au point un convertisseur analogique-numérique se distinguant par un con-20 trôle métrologique plus simple et une fiabilité plus élevée grâce à la représentation ambigue d'un même nombre de p-codes.

Ici et plus loin, on entend par p-code les p-codes Fibonacci et les codes de p-proportion "d'or".

Le problème posé est résolu par le fait que le convertisseur analogique-numérique comprenant (K-1) amplificateurs ayant chacun sa sortie reliée à l'entrée correspondante (depuis la deuxième à la K-ème)  $\mathcal{F}_{\mathrm{constant}}^{\mathrm{constant}}$  d'un commutateur analogique dont la sortie est cou-30 plée à l'entrée d'un comparateur à seuils multiples, l'entrée de l'(i+1)-ème amplificateur étant connectée à la sortie de l'i-ème amplificateur, la première entrée du premier amplificateur étant couplée à la première entrée du commutateur analogique, celle-ci 35 servant d'entrée au convertisseur analogique-numérique, la seconde entrée du premier amplificateur étant reliée

à la sortie du convertisseur numérique-analogique, la première, la deuxième et la troisième sorties d'une unité de commande étant couplées aux entrées de commande respectivement du commutateur analogique, 5 du comparateur à seuils multiples et d'un registre, est caractérisé, selon l'invention, en ce qu'il est muni d'un traducteur de code série ayant son entrée multiple reliée à la sortie multiple du comparateur à seuils multiples, d'un circuit de comparaison numé-10 rique, d'un compteur réversible, d'un commutateur numérique à l'entrée duquel est couplée la sortie du traducteur de code série, d'un compteur à la sortie multiple dont on a relié une unité de convolution et de développement du code, celle-ci ayant sa sortie 15 multiple couplée à l'entrée multiple du convertisseur numérique-analogique, d'un analyseur de code et d'une unité de détermination du type de développement du code et d'une unité de détermination du type de développement du code, la première entrée multiple de 20 cette dernière étant connectée à la sortie multiple de l'unité de convolution et de développement du code et la seconde entrée multiple étant reliée à la sortie multiple du registre, l'entrée de celui-ci étant réunie avec la sortie de l'analyseur de code, ce 25 dernier ayant son entrée multiple associée à la sortie multiple du compteur, la sortie à K bits du commutateur numérique étant couplée aux entrées du compteur et du compteur réversible, la sortie multiple de ce dernier, qui sert de sortie au convertisseur analo-30 gique numérique, étant connectée à l'entrée multiple du circuit de comparaison numérique, la sortie de celui-ci étant couplée à la première entrée de commande de l'analyseur de code, la seconde entrée de commande de ce dernier ainsi que les entrées de commande de l'unité de convolution et de développement du code, du compteur réversible et du commutateur numérique

étant couplées respectivement aux quatrième, cinquième, sixième et septième sorties de l'unité de commande, l'entrée de cette dernière étant mise en liaison avec la sortie de l'unité de détermination du type de développement.

Une telle conception du convertisseur selon l'invention permet de simplifier son contrôle métrologique de même que d'accroître sa fiabilité.

D'autres caractéristiques et avantages de l'in-10 vention seront mieux compris à la lecture de la description qui va suivre et en se référant aux dessins annexés dans lesquels :

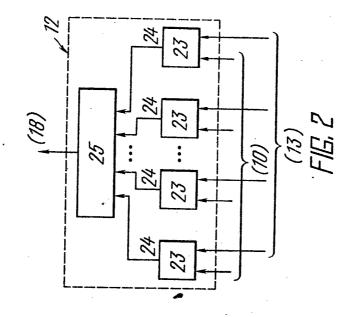

- la figure 1 représente le schéma synoptique général du convertisseur analogique-numérique selon l'invention;

15

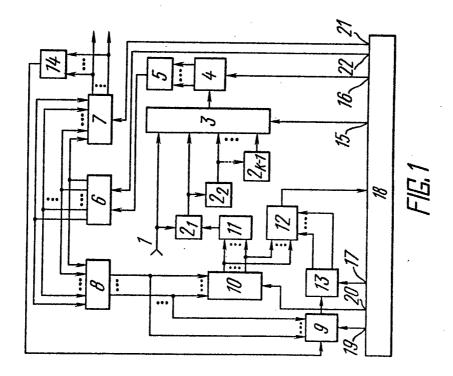

- la figure 2 représente un exemple de réalisation de l'unité de détermination du type de développement selon l'invention.

Le convertisseur analogique-numérique faisant

l'objet de l'invention tel qu'il est représenté à la

figure 1 comprend une entrée 1 à laquelle on applique

la grandeur analogique à traduire, des amplificateurs

2 au nombre de K-1 ayant chacun sa sortie reliée à

l'entrée correspondante, depuis la deuxième à la

N-ème, d'un commutateur analogique 3. L'entrée de

l'amplificateur 2; est associée à la sortie de

l'amplificateur 2; La première entrée du premier

amplificateur 2; et la première entrée du commutateur

3 sont couplées à l'entrée 1. La sortie du commutateur analogique 3 est associée à l'entrée d'un comparateur 4 à seuils multiples qui traduit la grandeur

analogique en code unitaire parallèle. La sortie multiple dudit comparateur 4 est reliée à l'entrée mul-

35 le code unitaire parallèle en code unitaire série. La sortie du traducteur 5 est associée à un commuta-

tiple d'un traducteur 5 de code série qui traduit

teur numérique 6 dont la sortie à K bits est couplée à un compteur réversible 7 et à un compteur 8. La sortie multiple de ce dernier est connectée à l'entrée multiple d'un analyseur de code 9 ayant pour fonction de déterminer le numéro du bit significatif supérieur du code à analyser d'une part et à l'entrée multiple d'une unité 10 de convolution et développement du code d'autre part.

Suivant le mode préféré de réalisation, l'unité

10 10 est un dispositif de réduction de p-codes Fibonacci

à la forme minimale (voir brevet Grande-Bretagne

N° 1543302).

La sortie multiple de l'unité 10 est mise en liaison avec un convertisseur numérique-analogique 15 11 qui, lui, a sa sortie réunie à la seconde entrée du premier amplificateur 2<sub>1</sub>.

Outre ceci, la sortie multiple de l'unité 10 est reliée à la première entrée multiple d'une unité 12 de détermination du type de développement. Cette 20 unité permet de déterminer le type de développement opéré par l'unité 10.

La seconde entrée multiple de l'unité 12 est connectée à un registre 13.

Ce dernier sert à stocker les numéros des bits

25 défaillants. L'entrée du registre 13 est raccordée

à l'analyseur 9, celui-ci ayant sa première entrée

de commande de liaison avec la sortie d'un circuit

14 de comparaison numérique ayant pour rôle de comparer le signal d'entrée aux grandeurs étalons et de

30 produire le signal annonçant que le code a dépassé

la valeur de consigne.

L'entrée multiple du circuit 14 est couplée à la sortie multiple du compteur réversible 7, cette sortie constituant celle du convertisseur analogiquenumérique qui fait l'objet de l'invention.

Les entrées de commande du commutateur analogique

3, du comparateur 4 à seuils multiples et du registre 13 sont couplées à la première, à la deuxième et à la troisième sorties respectivement 15, 16 et 17 d'une unité de commande 18. D'autre part, la seconde entrée de commande de l'analyseur de code 9 ainsi que les entrées de commande de l'unité 10 de convolution et développement, du compteur réversible 7 et du commutateur numérique sont connectées aux quatrième, cinquième, sixième et septième sorties respectivement 19, 20, 21 et 22 de l'unité 18.

On a relié à l'entrée de ladite unité 18 la sortie de l'unité 12 de détermination du type de développement.

L'unité 12 est réalisée généralement sous forme 15 d'un circuit logique combinatoire comme par exemple celui qui est donné à la figure 2.

Dans ce cas, l'unité 12 comporte des circuits logiques 23 "ET" en nombre égal à celui des bits du code, la sortie 24 de chacun des circuits 23 étant 20 connectée à l'entrée correspondante d'un circuit 25 "OU", la sortie de ce dernier constituant celle de l'unité 12. Les premières entrées des circuits 23 forment la première entrée multiple de l'unité 12 qui est connectée à la sortie multiple de l'unité 25 10 alors que les secondes entrées desdits circuits 23 forment la seconde entrée multiple de l'unité 12 couplée à la sortie multiple du registre 13.

Le fait d'introduire de nouveaux éléments tels que le traducteur 5, le commutateur 6, les compteurs 7 et 8, les unités 9, 10, 12, 13, 14, le fait aussi d'introduire de nouvelles liaisons permet de rendre plus simple le contrôle métrologique en exploitant le caractère ambigu de représentation codée d'un même nombre. On obtient par ailleurs un accroissement de la fiabilité du convertisseur analogique-numérique

proposé en écartant, au cours du codage, les bits défaillants.

Il convient de noter ici que la défaillance d'un bit peut être de deux espèces.

Premièrement, lorsque la grandeur étalon ne peut pas être utilisée complètement pour former la grandeur analogique de sortie, il y a défaillance du type de "non mise en circuit" (défaillance cataleptique).

Deuxièmement, lorsque la grandeur étalon qui forme le signal analogique de sortie n'est pas proportionnelle au poids du bit du code, il y a défaillance du type de "déréglage" (défaillance paramétrique).

15 Le convertisseur analogique-numérique faisant l'objet de l'invention fonctionne en deux régimes : régime de conversion directe de la grandeur analogique en numérique et régime de contrôle métrologique.

20 La conversion de la grandeur analogique d'entrée en p-code à <u>n</u> bits s'opère en <u>k</u> cycles. A chacun des cycles, il est formé <u>m</u> bits du code. L'i-ème cycle s'effectue avec la participation de i-l amplificateurs 2, du convertisseur numérique-analogique 11,

25 de l'i-ème canal du commutateur analogique 3, de l'i-ème canal du commutateur numérique 6 et des autres éléments du convertisseur selon l'invention à l'exception de l'analyseur 9 et du circuit 14. Le régime de contrôle métrologique est réalisé avec 30 la participation de l'ensemble des organes.

Comme on l'a déjà dit, on entend par p-codes les p-codes Fibonacci et les codes de p-proportion "d'or".

On appelle p-code Fibonacci la notation de tout 35 nombre naturel N sous forme de :

$$N = \sum_{i=0}^{n} a_i \Psi_{\rho} (i),$$

a: € {0,1}

$\Psi_{

ho}$ : poids de l'i-ème bit ou i-ème nombre p Fibonacci a calculer comme suit :

10 Dans le code de p-proportion "d'or" tout nombre réel D est représenté ainsi :

$$D = \sum_{l=-\infty}^{+\infty} a_l d_p^l$$

15 pour  $a_{\ell} \in \{0,1\}$   $\alpha_{p}^{\ell}$ : poids de  $\ell$ -ème bit. p = 0,1,2...

25

Il y a pour un même nombre un ensemble de repré sentations du genre donné parmi lesquelles il existe une 20 forme unique que l'on appelle minimale caractérisée par la présence, à droite de chaque unité, d'au moins p zéros. Lorsque p = 0 le code de p-proportion "d'or" coincide avec le code binaire classique.

$x^{p+1} = x^p + 1$

Les poids des bits du code sont liés entre eux par le rapport récurrent suivant:  $\alpha_{p}^{\ell} = \alpha_{p}^{\ell} + \alpha_{p}^{\ell-(p+1)}$

qui est à la base de l'opération de convolution et de développement des bits du code. La convolution consiste à substituer à zero dans le l'eme bit et aux unités dans les (l-1)-ème et (l-p-1)-ème bits leur népation, elle est désignée par 💯.

Le développement est une opération inverse de la 35 convolution et consite à substituer à l'unité du l'eme bit et aux zéros des (l-1) et (l-p-1)-ème bits leur négation, il est désignée par 🖽

La particularité essentielle de ces opérations réside en ce qu'elles ne modifient pas la valeur du nombre représenté par le code, mais seulement la forme de représentation du code.

5 Mis en régime de conversion directe de la grandeur analogique d'entrée en p-code, le dispositif fonctionne de la manière suivante. Durant le premier cycle, la grandeur analogique à traduire provenant de l'entrée 1 est appliquée à la première entrée du com-10 mutateur 3 qui, obéissant à un signal de commande venant de l'unité 18, la transmet à l'entrée du comparateur 4 à seuils multiples. Ce dernier transforme la grandeur analogique d'entrée en code parallèle que le traducteur 5 traduit en code unitaire série. Le code 15 unitaire série est envoyé, par l'intermédiaire du commutateur 6, aux entrées des compteurs 7 et 8. En deuxième cycle, le p-code est transmis du compteur 8 à l'unité 10, cette dernière réalisant, sous l'action de signaux parvenant de l'unité 18, le changement de 20 la forme de représentation du code. Recevant une combinaison de code comportant des zéros dans les bits défaillants, l'unité 12 produit un signal qui, appliqué à l'unité 18, fait cesser la formation des signaux de commande. Les numéros des bits défaillants sont déterminés au cours du contrôle métrologique. Quittant l'unité 10, le code attaque l'entrée du convertisseur numérique-analogique 11. La grandeur analogique correspondant à ce code est prélevée sur la sortie dudit convertisseur numérique-analogique 11 et appliquée à 30 la seconde entrée de l'amplificateur 2<sub>1</sub> tandis que la ·première entrée de celui-ci reçoit la grandeur d'entrée à traduire. La différence AI de ces grandeurs est amplifiée par l'amplificateur 2, de M fois et est envoyée à la seconde entrée du commutateur 3. Sous l'ac-35 tion du signal de commande venant de l'unité 18, la grandeur M. A I est transmise à l'entrée du comparateur

Le code unitaire parallèle correspondant à cette grandeur est traduit, par le traducteur 5, en code unitaire série qui est envoyé, par l'intermédiaire du commutateur numérique 6, aux entrées du compteur 5 8 et du compteur 7. C'est ainsi que l'on ajoute au contenu des compteurs 7 et 8 le résultat de conversion de deuxième cycle. En troisième et quatrième cycles, le convertisseur analogique-numérique fonctionne de manière analogue en mettant en jeu les amplificateurs 2 et 2 respectivement au troisième et quatrième cycles.

Examinons le fonctionnement du convertisseur analogique-numérique en régime de contrôle métrologique.

On fait commencer le contrôle en vérifiant si le (p+2)-ème bit du convertisseur analogique-numérique correspond à ses caractéristiques métrologiques. On suppose que p+1 bits inférieurs sont en bon état.

On applique, à l'entrée 1 du convertisseur analogique-numérique, une grandeur analogique en accrois-20 sement étagé dont l'i-ème échelon est utilisé pour vérifier l'i-ème bit. Le contrôle de tout bit se fait en deux étapes.

A la première étape, on réalise la transformation de la grandeur en code par le procédé qui vient d'être 25 décrit.

A la seconde étape, il y a encore codage de la grandeur de l'échelon donné avec cette différence que le bit significatif supérieur du code est exclu par développement du code dans l'unité 10. Par exemple, 30 la combinaison de code 00100100 contenant une unité au 6-ème bit (significatif supérieur) est remplacée par la combinaison 00011011. Le compteur réversible 7 fonctionne en régime de soustraction. En fin de conversion de la grandeur analogique d'entrée en code, 35 on obtient, dans le compteur réversible 7, le code d'erreur du bit à contrôler représentant la différence

de deux représentations de code d'une même grandeur analogique. Si le code d'erreur est supérieur à la valeur de consigne, le circuit de comparaison numérique 14 formera un signal qui sera appliqué à la première entrée de commande de l'analyseur de code 9. Ce dernier détermine le numéro du bit significatif supérieur du code en provenance du compteur 8. Sous l'action du signal envoyé de l'unité 18 de commande le numéro de bit reconnu défaillant est placé au registre 13.

Sur ce, le contrôle métrologique du bit donné prend fin.

Le fait d'introduire de nouveaux éléments et de nouvelles liaisons rend plus simple le contrôle métro15 logique grâce à l'automatisation de ce processus. On constate par ailleurs une tolérance moins sévère quant à la précision des grandeurs étalons d'entrée dont les écarts sont possibles dans une marge de  $Q_1 + \frac{1}{3}Q_{1-p}$  à  $Q_1 + \frac{2}{3}Q_{1-p}$  (avec  $Q_1$  et  $Q_{1-p}$ : respectivement poids de l'i-ème et du (i-p)-ème bats).

On voit croître aussi la fiabilité du convertisseur analogique-numérique grâce à l'exclusion de q bits défaillants au cours du codage. La valeur la plus grande de q est déterminée suivant la condition :

$$S_n - S_n^* \geqslant S_n$$

30

pour  $s_n$  - somme des poids de tous les  $\underline{n}$  bits du code ;  $s_n^*$  - nombre maximal pouvant être représenté sous forme minimale à l'aide de  $\underline{n}$  bits ;  $s_p$  - somme des poids de tous les  $\underline{q}$  bits défaillants.

Cette dernière particularité permet d'augmenter le pourcentage des produits finis en cas de fabrication en série des convertisseurs analogiques-numériques sous forme de grands circuits intégrés en inscrivant au nombre des produits faits les convertisseurs n'ayant

pas plus de g bits défaillants.

Bien entendu, l'invention n'est nullement limitée au mode de réalisation décrit et représenté qui

n'a été donné qu'à titre d'exemple. En particulier,

elle comprend tous les moyens constituant des équivalents techniques des moyens décrits ainsi que leurs

combinaisons, si celles-ci sont exécutées suivant son

esprit et mises en oeuvre dans le cadre des revendications qui suivent.

## REVENDICATION

Convertisseur analogique-numérique, comprenant K-1 amplificateurs (2i) ayant chacun sa sortie reliée à l'entrée correspondante (depuis la deuxième à la k-ème) 5 d'un commutateur analogîque (3) dont la sortie est couplée à l'entrée d'un comparateur (4) à seuils multiples, l'entrée de l'i+l-ème amplificateur étant connectée à la sortie de l'i-ème amplificateur, la première entrée du premier amplificateur étant couplée à la première 10 entrée du commutateur analogique, celle-ci étant l'entrée du convertisseur analogique-numérique, la seconde entrée du premier amplificateur étant reliée à la sortie du convertisseur numérique-analogique, la première (15), la deuxième (16) et la troisième (17) sorties d'une unité de commande (18) étant couplées aux entrées de 15 commande respectivement du commutateur analogique, du comparateur à seuils multiples et d'un registre (13), caractérisé en ce qu'il est muni d'un traducteur de code série (5) ayant son entrée multiple reliée à la 20 sortie multiple du comparateur à seuils multiples, d'un circuit de comparaison numérique (14), d'un compteur réversible (7), d'un commutateur numérique (6) à l'entrée duquel est couplée la sortie du traducteur de code série, d'un compteur(8) à la sortie multiple duquel on 25 a relié une unité de convolution et de développement du code (10), celle-ci ayant sa sortie multiple couplée à l'entrée multiple du convertisseur numérique-analogique, d'un analyseur de code (9) et d'une unité de détermination du type de développement (12), la première en-30 trée multiple de cette dernière étant connectée à la sortie multiple de l'unité de convolution et de développement du code et la seconde entrée multiple étant reliée à la sortie multiple du registre, l'entrée de celui-ci étant connectée à la sortie de l'analyseur de code, ce

dernier ayant son entrée multiple associée à la sortie multiple du compteur, la sortie à k bits du commutateur numérique étant couplée aux entrées du compteur et du compteur réversible, la sortie multiple de ce dernier, 5 qui sert de sortie au convertisseur analogique-numérique, étant connectée à l'entrée multiple du circuit de comparaison, la sortie de celui-ci étant couplée à la première entrée de commande de l'analyseur de code, la seconde entrée de commande de ce dernier ainsi que les 10 entrées de commande de l'unité de convolution et de développement du code, du compteur réversible et du commutateur numérique étant couplées respectivement aux quatrième (19), cinquième (20), sixième (21) et septième (22) sorties de l'unité de commande, l'entrée de 15 cette dernière étant mise en liaison avec la sortie de l'unité de détermination du type de développement.